Using the VLAB

Using Vivado over the VLAB

First connect to a VLAB board, as above:

./vlab.ky -k mykey

If you are running Vivado on a remote server, ensure that you also run the VLAB scripts on that server (not on your local computer). Now in Vivado click "Open Hardware Manager" in the Flow Navigator in the left-hand column. Then click "Open Target" | "Open New Target" in the Flow Navigator. In the Open wizard click Next, select Remote Server, Next, and use the following settings:

Hostname: localhost Port: 12345

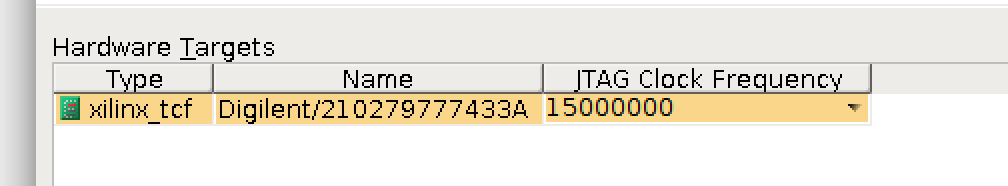

Click Next and the tools should connect and see a Zybo Z7:

Click Next and Finish. You can send bitfiles to the FPGA by selecting Program Device from the Flow Navigator.

The process in SDK is similar. In the bottom left should be a Target Connections panel (Window -> Show View -> Other if it is not visible.) Click Add New Target Connection. Set the name to VLAB and the host and port as above, and click OK. To use this new connection you need to set your Run Configuration to use it. In the menus select Run -> Run Configurations and for the configuration you are using change the connection to the VLAB. This will allow you to upload code, bitfiles, and use the debugger all remotely.

Exiting the VLAB

Please close your VLAB connection when you are not using it so that other students can use the board (remember that your exclusive lock on a board will expire ten minutes after connecting anyway.).

The VLAB terminal window is running screen. To close it, press and release Ctrl-a, then press 'k' and confirm with 'y'.

When using a Virtex FPGA board (or anything other than a Zynq), errors following the line "fpga configuration failed. DONE PIN is not HIGH" when disconnecting are normal, and can be ignored (we will tidy this up one day...).

Connecting through the SSH Gateway

Due to the university's firewall rules, the virtual lab relay server (rts001.cs.york.ac.uk) is only accessible from departmental machines (including student compute servers, staff Linux compute servers, anything on the RTS lab network, and all student lab PCs), or via the IT Services SSH service. Therefore, when off campus or using eduroam, the easiest way to access the VLAB (and other departmental servers) is through the IT Services SSH gateway. You will need to request access to this service before you can use it - see https://www.york.ac.uk/it-services/services/ssh/ for more information.

Once you have been granted access to the SSH gateway, the following SSH rules can be used to connect directly through to the VLAB by adding them to the ~/.ssh/config file on the computer you're connecting from.

Host ssh.york.ac.uk User YOUR_ITSERVICES_USERNAME Host rts001.cs.york.ac.uk User YOUR_VLAB_USERNAME ProxyCommand ssh -A -T -o Compression=no ssh.york.ac.uk -W %h:%p

The SSH gateway server also accepts key-based authentication, using the ~/.ssh/authorized_keys file from your standard university Linux home directory.

Graphical Output over the VLAB

Viewing HDMI output is not natively supported by the VLAB. However, it is possible to use Xilinx's USB debugging interface to download the contents of the video frame buffer straight out of the FPGA and view that. Because USB debugging is rather slow, and the video frame is uncompressed it take take a while (around 16 seconds) to pull an entire video frame. However this might still be useful to get an idea for how your code is progressing.

Note that this script assumes that you are running on Linux because it uses ImageMagick and the Gnome Image Viewer. These can be installed on a Debian-based Linux with the following:

> sudo apt-get install eog imagemagick

You can avoid installing Eye of Gnome by switching the image viewer the script uses. On the "exec eog $filename.png" line, switch eog to (for example) gwenview for KDE or open for macOS.

The first task is to get the memory address of the video frame you want to view. In the HDMI example code which you are probably working with, two frame buffers are set up with the following code.

u32 frameBuf[DISPLAY_NUM_FRAMES][MAX_FRAME] __attribute__((aligned(0x20))); // Frame buffers for video data void *pFrames[DISPLAY_NUM_FRAMES]; // Array of pointers to the frame buffers

This is called multiple buffering and allows the video hardware to be drawing one frame to the screen, whilst the CPU is preparing the next frame. You can get the memory address of a frame by simply printing it out to the console.

printf("Address of frame: %p\n", pFrames[0]);

In the HDMI example this will be 0x11ce80 but this is likely to change frequently as you edit your code. Once you have the address of the frame you are interested in, download this script:

In XSDK's menus, select Xilinx | XSCT Console to view the debugging interface. The XSCT console has the promt xsct%. Set the target address of frame and then run the script.

xsct% set base 0x11ce80 xsct% source /path/to/videograb.tcl

This will fetch the frame, convert it to a PNG, and show it in an image viewer. By default the script only grabs every 20th line, but to make it grab the entire frame set the following:

xsct% set stride 1